写在前面:

通过控制MOS上、下管的导通与关闭,让电容重复的工作于充电、放电状态,观察电容瞬间放电时的最大电流值。通过仿真软件,研究不同形式的大面积铺铜(PADS的术语:pour)所带来的电容放电的最大电流值。该电路的目的和意义在于研究并验证在同一种MOS管和电容值下(不考虑器件彼此细微的参数差异所引起的结果),仅因PCB Layout的差异而带来的不同的放电电流值。由仿真软件计算的结果来提供改进方向,并实物制造,最终观察结果。

该结果同时也阐明了数字IC工作时所产生的噪音,是如何传递并影响到其它器件,是如何导致电子产品辐射超标(IEC61000 及GB/T 17626标准)。

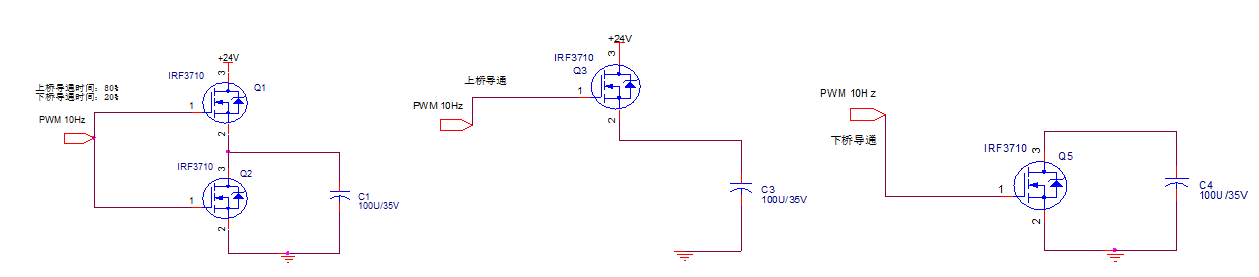

(图1)基本电路原理图 (图2)对电容充电 (图3)电容放电

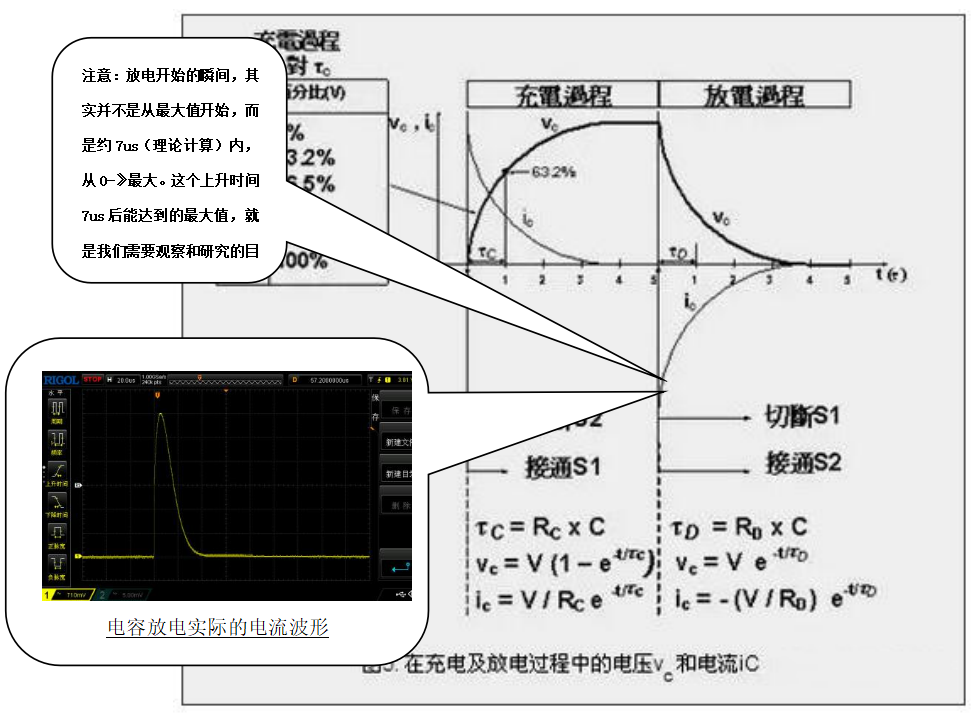

图4为电容充电、放电的理论和放电电流的计算公式;

(图4)

欧姆定律I=U/R,适合一切电路,无论暂态还是稳态。故在电容端电压一定的情况下,想要提升放电电流,必须降低环路总电阻。环路总电阻包括:MOS管的导通电阻、电容的ESR,PCB的铜箔走线电阻。MOS管和电容是固定不变的。因此要想获得更大的瞬间放电电流,毫无疑问,要想办法如何去降低整个PCB铜箔走线的电阻。增加铜箔的厚度,固然可以降低电阻,但那要极大的增加成本,不是本文要研究的。本文研究的是靠仿真软件来优化电容放电时电流的走势来达到降低电阻值。实物制造及测试的结果也证实如此。

对该电容大电流放电走线的研究,带来了一个意外的收获:让我们更清晰的看到了,PCB上的器件噪音是如何产生的,而这噪音,不单单会干扰到同一pcb上的其它器件①,还是引起了电路板辐射的关键因素。(图5示意如何制作一个4G/5G全向pcb天线;)

(图5)

准备工作:电流传感器(探头)

为了能在示波器上准确、实时的显示电流变化的瞬时曲线,需要一个电流探头,当然可以用示波器原配件。考虑到价格因素,我们选用一个霍尔电流传感器,来搭建成测试平台。

不同的厂家、不同器件,不同的设计思路,会有不同的响应时间和精度,要从现有的开环、闭环的霍尔电流传感器中挑选出符合以下要求的器件:响应时间极短(<1μs @ di/dt > 50A/μs,精度优于0.2%)。以下几款芯森电子的闭环霍尔和开环霍尔传感器均符合要求,分别展示了其响应时间和外观。

下列图中,电流发生器的产生峰值电流约为360A ,0最大值的上升时间约为7μs。

响应时间<0.3μs(图6) 外观图(CN2A H00)(图7)

响应时间<1μs (图8) 产品外观图(CM4A H00)(图9)

响应时间<1μs(图10) 产品外观图(CR2A)(图11)

开环,响应时间<5μs(图12) 产品外观图(HS1V)(图13)

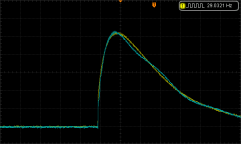

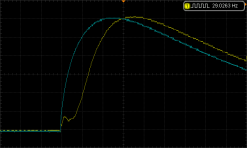

为方便测量,最终选择了一款高精度、闭环、电流输出式的霍尔电流传感器件,型号为:CM4A H00,电流测量范围是1000A。再来验证一下,使用CM4A对电容充电时候的原边/副边的对应波形,见图14;

(图14)

黄线:原边电阻0.01R的无感电阻两端波形。

蓝线:CM4A输出的波形,负载为47R 插件电阻。

因为电源内阻和容量原因,无法提供很大的输出电流,所以是一个振荡的曲线;从波形来看,匹配的很好,这说明,采用CM4A来观察电容放电的波形,其数据可信。

如何获得更大的放电电流

为了确保测量的准确性,基于所选电容的容值(100u)和ESR值,估算出电容充电到最高值的时间。计算公式表明是5*RC,(公式中,R=充电回路的总电阻,C=电容的容值),大约为0.5ms。受制于电源等因数,结合不断测试,最终确定为:每次对电容的充电时间为保证为至少80ms,确保各种电容(<2200u)都能完全充足。

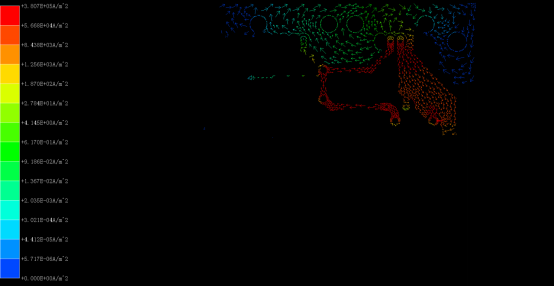

分析pcb layout对电容放电的影响,这需要通过对原始的pcb文件做电磁仿真的电流云图去实现,最终是找到了在同一种MOS,同一个品牌和容值下,同一个电容充电电压下和温度条件下,有一种最大放电电流。

该设计一共进行了三次,实物制造了2次,用于实物评估,第三版仍在不断的仿真改进。

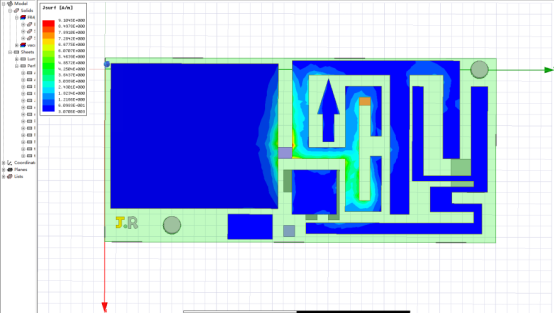

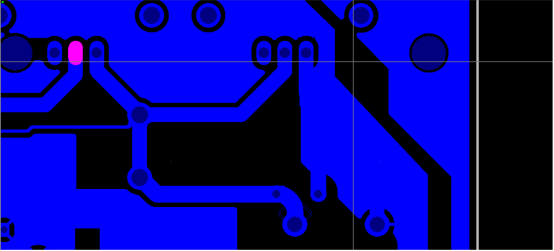

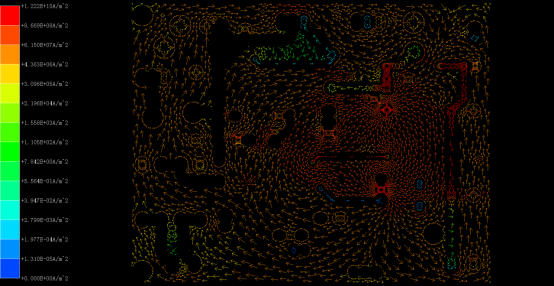

现在分别展现第三版、第二版、第一版本的pcb layout及对pcb原始文件电流密度的仿真结果。

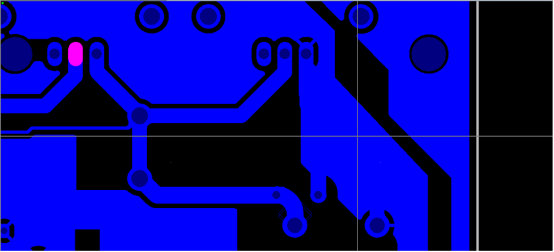

图15-16展示了第三版,改进中,正在不断的仿真<-->改pcb layout。

(图15)

第三版 Max=3.807x105A/m2(图16)

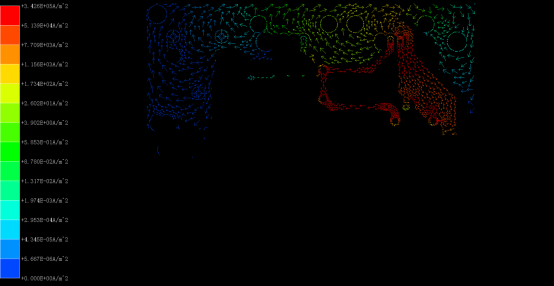

图17-18展示了第二版:

(图17)

第二版Max= 3.426x105 A/m2(图18)

第二版电容电压为12V时候,100u/100v的固态电容最大放电电流可以达到87A 。

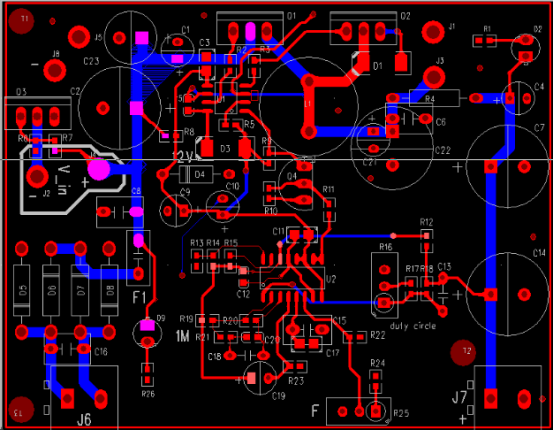

图19-20展示了第一版:

(图19)

电流密度 MAX=1.222X1010 A/M2(图20)

第一版的电容电压为12V时候,100u/100v的固态电容最大放电电流可以到104A

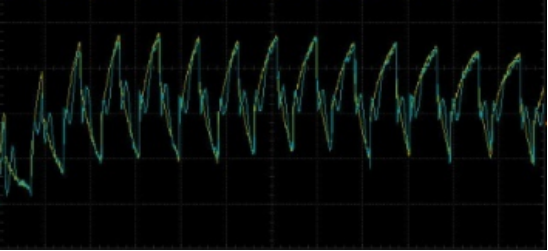

实际测试来看,同一种IRF3205的MOS,同为100u/100v,固态电容,从分析电流密度图来看,第一版应该要比第二版要好,实际测试情况也是如此(见下图中,MAX: 431mV / 506mV),即:7μs达到的最大值,第一版要好过第二版,计算来看,大约是好506/431=1.17倍。下述的测量,基于CM4A H00器件和RIGOL 100Mhz的示波器,电容电压为12V;

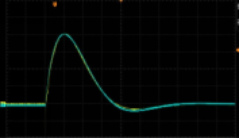

第二版的电流放电波形(图21) 第一版的电流放电波形(图22)

现在,基于第二版的电路,研究几种不同的电容放电波形,分别是固态电容的100u/25v、铝电解电容的100u/25v、2.2u/25v X5R 0805、4.7u/100v的CBB电容,及固态电容的100u/25v+2.2u/25v X5R 0805 并联,共5种波形。

这种测试的现实意义在于,观察用于耦合为目地的电容,如何应用为最优。

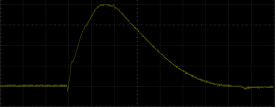

1、下图23,铝电解电容100u/25v:4μs到最大值,拖尾很长

(图23)

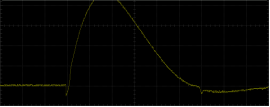

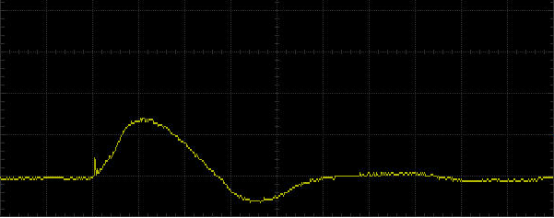

2、下图24,固态电容100u/25v:约6.5μs到最大;

(图24)

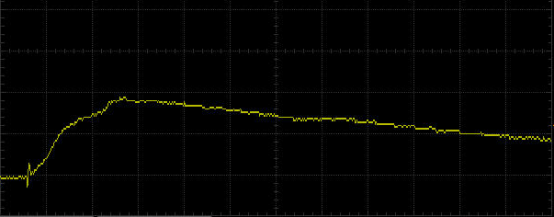

3、下图25,4.7u/100v CBB:

(图25)

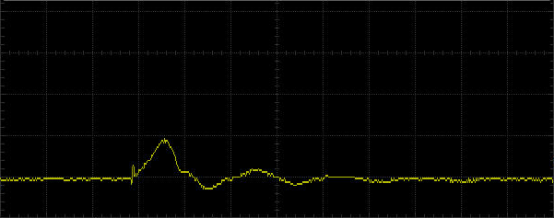

4、下图26,2.2u/25v X5R 0805:以近似一条直线的方式到最大,且有振荡现象;

(图26)

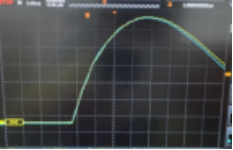

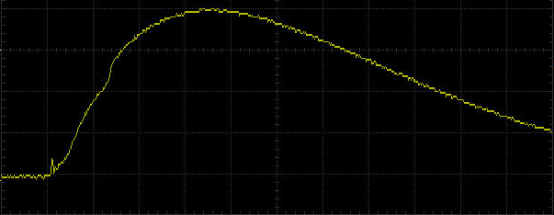

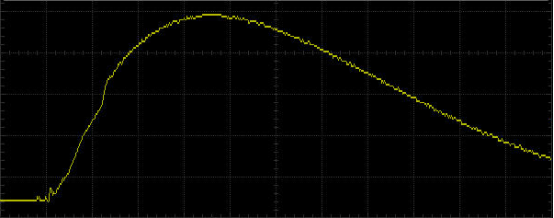

5、下图27,固态电容的100u/25v+2.2u/25v X5R 0805:可见,到最大值的时间稍微改变,约7μs,但是最大值提高了774mV-->850mV,提高了约10%。

(图27)

从上述几张测试图能够看出,固态电容的放电效果非常好。2.2μF X5R电容的放电表现也可以,不过鉴于其容值较小,难以与固态电容形成显著的对比效果,且目前手头没有22μF的MLCC电容用于进一步测试对比。

当然,固态电容加MLCC是可以提高放电电流,但提升幅度有限;并且,从测试曲线分析可知,并联电容会使系统到达电流最大值的时间延长约0.5μs,综合考量,对于MCU/GPU等芯片,在其Vcc - Gnd之间放置耦合电容时,采用单一电容更为适宜。