はじめに:

MOSの上管と下管のオン・オフを制御することで、コンデンサを充電・放電状態において繰り返し動作させ、コンデンサの瞬間的な放電時の最大電流値を観察します。シミュレーションソフトウェアを用いて、異なる形式の大面積銅箔(PADS用語:pour)がコンデンサの放電最大電流値にどのような影響を与えるかを研究します。この回路の目的と意義は、同一のMOS管およびコンデンサ値(個体差による微細なパラメータの違いは無視)において、PCBレイアウトの違いのみによって生じる放電電流値の差異を研究・検証することにあります。シミュレーションソフトによる計算結果から改善方向を示し、実際に試作して最終的な結果を観察します。

また、この結果は、デジタルICの動作時に発生するノイズがどのように伝播し、他の部品に影響を与えるか、ならびに電子製品の放射規格超過(IEC61000およびGB/T 17626基準)を引き起こす要因を明らかにするものです。

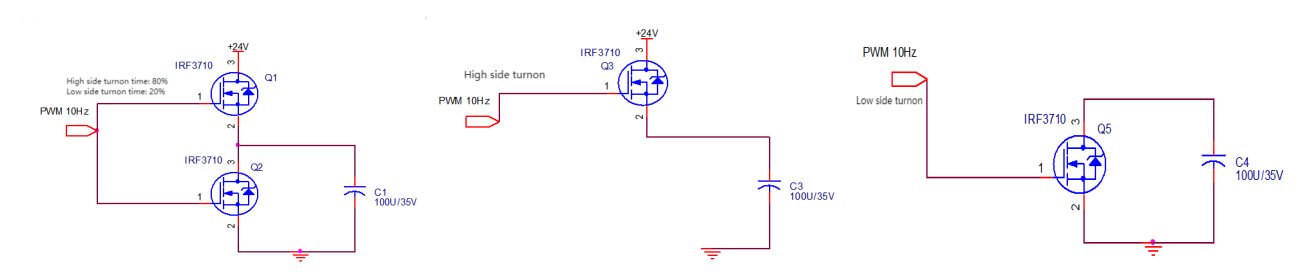

(図1)基本回路原理図 (図2)コンデンサへの充電 (図3)コンデンサの放電

図4は、コンデンサの充電・放電の理論および放電電流の計算式を示しています。

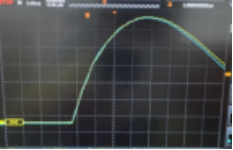

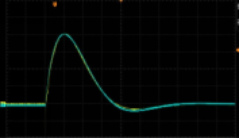

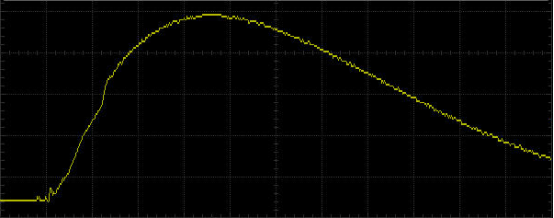

コンデンサ放電の実際の電流波形

注意:放電開始の瞬間は、実は最大値から始まるのではなく、約7μs(理論計算)の間に0から最大値へと上昇します。この7μs後に到達する最大値こそが、私たちが観察・研究すべき目標です。

(図4)

オームの法則 I=U/R は、過渡状態であれ定常状態であれ、すべての回路に適用されます。したがって、コンデンサ端子電圧が一定である場合、放電電流を増大させるには、ループ全体の抵抗を低減する必要があります。ループ総抵抗には、MOS管のオン抵抗、コンデンサのESR、PCBの銅箔配線抵抗が含まれます。MOS管とコンデンサは固定されているため、より大きな瞬間放電電流を得るには、PCB銅箔配線の抵抗をいかに低減するかが鍵となります。銅箔の厚さを増すことも抵抗低下につながりますが、コストが大幅に増加するため、本研究の対象外とします。本研究では、シミュレーションソフトウェアを用いてコンデンサ放電時の電流経路を最適化することで抵抗値を低下させる方法を追求します。実機製作およびテストの結果もこれを裏付けています。

この大容量コンデンサの放電配線に関する研究は、予期せぬ副産物をもたらしました。それは、PCB上の部品ノイズがどのように発生するかをより明確に理解できるようになったことです。このノイズは、同一PCB上の他の部品①を干渉するだけでなく、基板からの電磁放射を引き起こす主要因でもあります。(図5は、4G/5G用の無指向性PCBアンテナの作成方法を示しています。)

(図5)

準備作業:電流センサー(プローブ)

オシロスコープ上で電流変化の瞬時曲線を正確かつリアルタイムに表示するには、電流プローブが必要です。もちろん、オシロスコープ付属のプローブ也可以使用できますが、価格面を考慮し、ホール電流センサーを使用してテストプラットフォームを構築することにしました。

メーカーやデバイス、設計思想によって応答時間や精度は異なります。既存の開ループおよび閉ループ型ホール電流センサーの中から、以下の要件を満たすデバイスを選定する必要があります:応答時間が極めて短い(<1μs @ di/dt > 50A/μs)、精度が0.2%未満。以下の芯森電子製の閉ループおよび開ループホールセンサーはいずれも要件を満たしており、それぞれの応答時間と外観を示しています。

以下の図では、電流発生器によって生成されるピーク電流は約360A、最大値までの立ち上がり時間は約7μsです。

測定を容易にするため、最終的に高精度・閉ループ・電流出力型のホール電流センサー(型番:CM4AH00、電流測定範囲1000A)を選択しました。次に、CM4AH00を使用してコンデンサ充電時の一次側/二次側の対応波形を確認します(図14参照)。

(図14)

黄色線:一次側の無誘導抵抗(0.01Ω)両端の波形

青色線:CM4AH00の出力波形(負荷は47Ωの挿入抵抗)

電源の内部抵抗および容量の制約により、大きな出力電流を供給できないため、振動する波形となっていますが、波形から良好な一致が確認でき、CM4AH00を用いたコンデンサ放電波形の観測データは信頼できることが示されました。

より大きな放電電流を得る方法

測定の精度を確保するため、選択したコンデンサの容量(100μF)およびESR値に基づき、コンデンサが最高値まで充電される時間を算出しました。計算式によれば5*RC(式中、R=充電回路の総抵抗、C=コンデンサ容量)となり、約0.5msです。電源などの制約および継続的なテストの結果、最終的に各コンデンサ(<2200μF)が完全に充電されるよう、充電時間を少なくとも80msに設定しました。

PCBレイアウトがコンデンサ放電に与える影響を分析するには、元のPCBファイルに対する電磁シミュレーションによる電流密度クラウド図を作成する必要があります。その結果、同一MOS、同一ブランド・容量のコンデンサ、同一充電電圧および温度条件下において、最大放電電流を得られるレイアウトが存在することが判明しました。

本設計は計3回実施され、実機評価用に2回試作を行いました。第3版は現在もシミュレーションによる改良を重ねています。

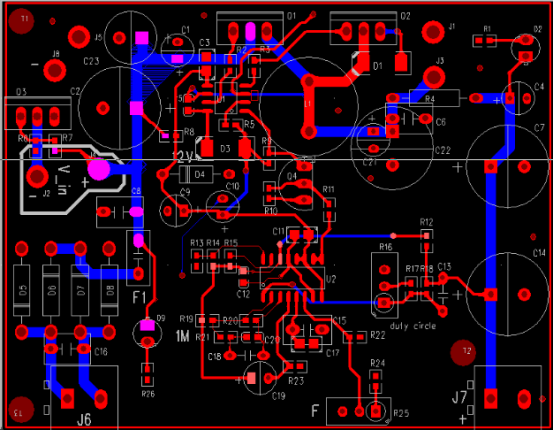

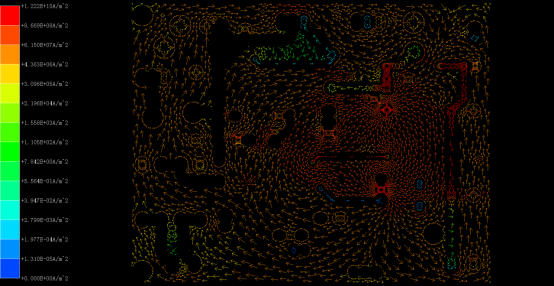

以下に、第3版、第2版、第1版のPCBレイアウトおよびPCB原ファイルに対する電流密度シミュレーション結果をそれぞれ示します。

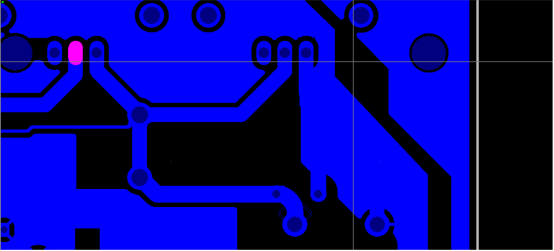

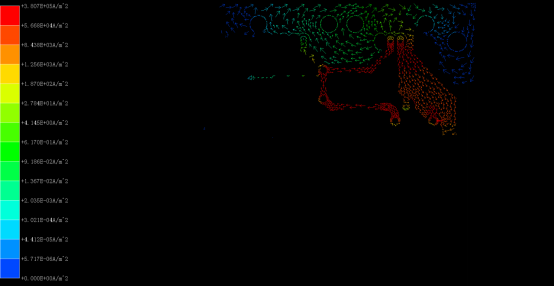

図15〜16:第3版(改良中、シミュレーション↔PCBレイアウト変更を繰り返し実施)

(図15)

第3版 Max=3.807×10⁵ A/m² (図16)

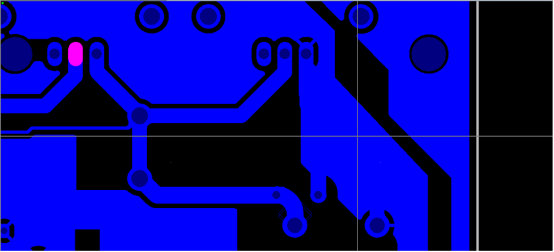

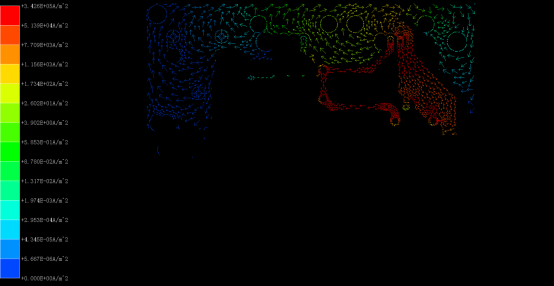

図17〜18:第2版

(図17)

第2版 Max=3.426×10⁵ A/m² (図18)

第2版では、コンデンサ電圧12V時、100μF/100Vの固体コンデンサの最大放電電流は87Aに達しました。

図19〜20:第1版

(図19)電流密度 MAX=1.222×10¹⁰ A/m² (図20)

第1版では、コンデンサ電圧12V時、100μF/100Vの固体コンデンサの最大放電電流は104Aに達しました。

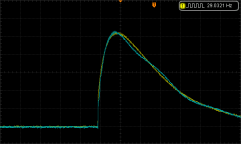

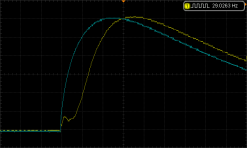

実際の実測結果によると、同一のIRF3205 MOS、同一の100μF/100V固体コンデンサにおいて、電流密度図の分析からは第1版の方が第2版より優れているはずであり、実測結果もそれを裏付けています(下記図参照、MAX: 431mV / 506mV)。すなわち、7μsで到達する最大値は第1版の方が第2版より良く、計算上は約506/431=1.17倍の差があります。以下の測定は、CM4AH00デバイスおよびRIGOL 100MHzオシロスコープを用い、コンデンサ電圧12Vで行いました。

次に、第2版の回路に基づき、いくつかの異なるコンデンサ放電波形を研究しました。具体的には、100μF/25V固体コンデンサ、100μF/25Vアルミ電解コンデンサ、2.2μF/25V X5R 0805、4.7μF/100V CBBコンデンサ、ならびに100μF/25V固体コンデンサ+2.2μF/25V X5R 0805の並列接続の計5種類の波形です。

このテストの現実的な意義は、カップリング目的で使用されるコンデンサの最適な適用方法を観察することにあります。

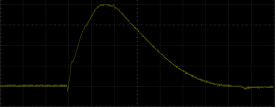

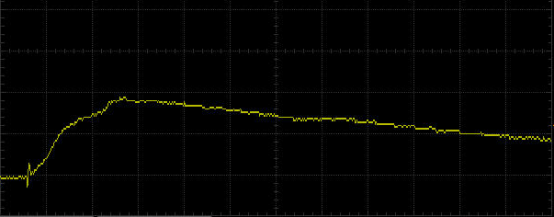

図23:アルミ電解コンデンサ100μF/25V → 4μsで最大値に到達、テールが非常に長い

(図23)

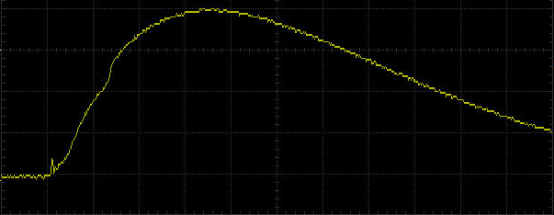

図24:固体コンデンサ100μF/25V → 約6.5μsで最大値に到達

(図24)

図25:4.7μF/100V CBBコンデンサ

(図25)

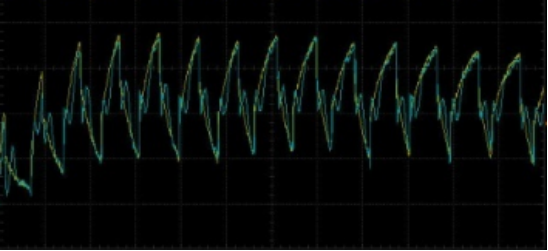

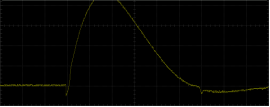

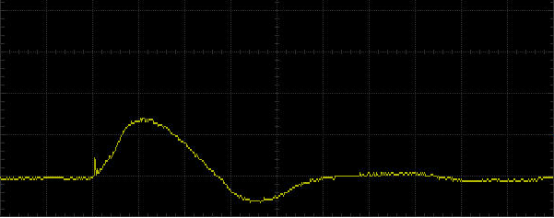

図26:2.2μF/25V X5R 0805 → ほぼ直線的に最大値に到達し、振動現象が見られる

(図26)

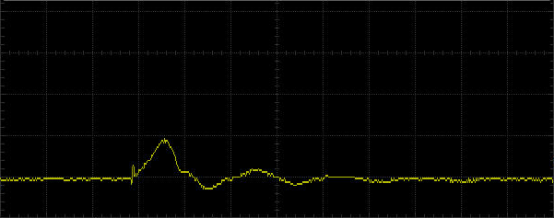

図27:100μF/25V固体コンデンサ+2.2μF/25V X5R 0805並列 → 最大値到達時間はわずかに変化(約7μs)するものの、最大値は774mV→850mVへ向上し、約10%の改善が見られた

(図27)

上記のテスト図から、固体コンデンサの放電性能が非常に優れていることがわかります。2.2μF X5Rコンデンサも放電特性は良好ですが、容量が小さいため固体コンデンサとの顕著な比較効果が得にくく、さらにテスト比較のために22μFのMLCCコンデンサが手元にない状況です。

もちろん、固体コンデンサにMLCCを並列接続することで放電電流を増加させることは可能ですが、その改善幅は限定的です。また、テスト曲線の分析から、コンデンサを並列接続するとシステムが電流最大値に到達するまでの時間が約0.5μs延長されることがわかります。総合的に判断すると、MCU/GPUなどのチップのVcc-Gnd間にカップリングコンデンサを配置する場合は、単一のコンデンサを使用することが適切です。